基于NAND Flash的高速大容量存储系统的设计(通讯)

基于NAND Flash的高速大容量存储系统的设计(通讯)

赵亚慧1,2, 金龙旭1, 陶宏江1, 韩双丽1, 张敏1,2

(1.小国科学院长春光学精密机械与物理研究所,长春130033;2.中国科学院大学,北京100049)

摘要:针对空间相机地面检测设备数据信息量大、存储速度快的特点,采用性能优良的NAND型Flash为存储介质,FPGA为控制核心,实现了高速大容量存储系统的设计。针对数据存储速度的提升,引入双plane操作、并行及流水线的方式控制Flash阵列。通过对Flash芯片中坏块特点的研究,引入了坏块管理部分。实验结果表明,该系统能够完成空间相机大量原始数据的高速记录工作,保证了数据记录的实时性及可靠性。

关键词:航空电子;空间相机;地面检测设备;存储系统;NAND Flash;并行技术

中图分类号:TP391 文章编号:1671 - 637X( 2016) 05 - 0071 - 05

0 引言

随着我国航空电子技术发展的日趋成熟,空间相机的数据采样率大幅度提升,为了实时、稳定地存储原始数据,空间相机数据存储系统的容量越来越大、存储速度也越来越快。而地面检测设备负责接收并存储相应数据便于后续分析处理,其存储速度必然要与空间相机数据存储系统的传输速度相匹配。为了保证记录数据的有效性,就对地面检测设备的性能提出了更高的要求。地面检测设备不但要将空间相机所记录的海量原始数据全部存储,还要做到实时连续快速存储,并且要保证数据的正确性。

高速大容量数据存储技术的发展主要由存储介质的发展构成。虽然传统的磁存储技术存储成本低,但其机械特性使得设备体积大、功耗高、易损坏,而地面检测设备需要经常在外场进行维护,磁存储技术显然不能满足设备携带方便和抗振动的要求。固态存储技术是以半导体芯片作为存储介质的数字存储技术,其设备不存在任何机械部件,环境适应能力强,已成为高速大容量数据存储系统设计方案的首选。

传统的高速大容量存储设备为了提高存储速度,在系统中增加存储芯片的使用数量,虽然操作简便,但是增加了设计成本;同时由于半导体芯片Flash存在无效块等存储特性,影响了系统的可靠性。

针对以上问题,本文以FPGA为中央控制核心,NAND型Flash为存储介质,并引入双plane操作、并行操作及流水线操作等存储关键技术,在满足系统设计指标要求的前提下减少Flash芯片使用数量,同时对Flash芯片建立坏块处理机制,提高系统可靠性,解决地面检测设备中的数据存储问题,完成数据高速海量存储。

1 系统总体结构设计

本系统针对空间相机地面检测设备,旨在解决系统中高速大容量的数据存储问题。系统具体的技术指标主要体现在:1)存储速度高,能实时连续记录高速原始数据,存储速度大于500 MB/s;2)存储容量大,能够存储海量数据,容量不低于600 GB;3)系统的可靠性高,误码率小。

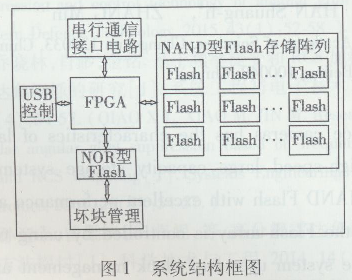

基于以上几个方面,本设计采用以FPGA为控制核心、Flash芯片为存储介质的方案。系统主要由FP-GA控制模块、Flash存储阵列、坏块管理模块、串行通信接口电路和USB控制模块几部分组成,见图1。

主控芯片是存储系统的核心器件,主要负责完成的任务有:产生Flash控制阵列时序、管理Flash坏块信息、实现通信接口等。这就要求相应的FPGA拥有足够的I/O数量用于数据传输,并有丰富的RAM资源便于缓存。综合考虑设计成本、系统功耗、适用范围等因素,主控芯片选择美国Xilinx公司高性能Spartan-6系列的XC6SLX100T,该芯片含有101261个逻辑单元,内置RAM容量多达4.71MB,为系统的逻辑设计提供了足够的缓存空间。

存储阵列模块主要负责完成系统的高速数据读写。Flash存储芯片作为半导体存储芯片具有密度高、容量大、抗震性能好等特点,成为本次存储系统中存储芯片的不二之选。

坏块管理模块是针对Flash芯片的坏块进行处理屏蔽,并将坏块信息写入非易失零出错的NOR型Flash芯片中进行保存,保证坏块信息的正确存储,降低系统的误码率。

串行通信接口电路用于数据传输,主要负责将空间相机的数据通过接口电路传送到地面检测设备。接口电路选用RS422标准,支持点对多的双向通信,抗干扰能力强。

USB接口模块的主要任务是方便与USB接口的外设进行通信。空间相机的数据传送到地面检测设备进行存储后,若PC机或其他带有USB接口的设备需要对数据进行后续分析处理,可以通过USB接口模块进行数据的高速传输。该模块接口芯片选用美国Cypress公司的CY7C68013,此款芯片满足USB2.0通信协议,功耗低、兼容性强。

2 系统关键技术

2.1 Flash阵列控制

根据Flash芯片采用的技术架构的不同,主要将其分为NOR型和NAND型。其中:NOR型Flash作为存储介质,可靠性高、随机读取性强,适合编程和擦除操作较少的代码存储;NAND型Flash存储密度高、读写擦除速度快,更适用于大量的数据存储的场合。

本设计主要针对地面检测设备的数据存储,需要将空间相机产生的大量数据传输并存储到地面检测设备中,因此选用NAND型Flash作为存储介质。美国镁光公司是著名的闪存生产公司,拥有SLC,TLC,MLC 3种结构的闪存芯片,其中:SLC型的Flash可靠性好,但是价格高、密度低;TLC型的Flash价格低,但使用寿命短,性价比低。根据本设计的技术要求,综合考虑芯片的密度、价格、使用寿命等因素,最终选取MLC型的NAND Flash作为本次设计的存储芯片,具体型号为MT29F512G08CUCAB。芯片数据宽度为8 bit,单片存储容量达到512 Gbit,共包含8个逻辑单元,每个逻辑单元包含2个plane,它们共用一套总线。每个plane由2048个块组成,每个块有256页,每页可以存储8192字节。该芯片能够完成复位、配置、编程、读以及擦除等多种操作类型,本设计主要用到编程操作以及读操作,此芯片完全能够胜任。

2.1.1 页编程操作

NAND型Flash的编程操作以页为单位进行。传统的页编程方式为单plane页编程操作:首先将写指令80H和地址写入相应寄存器,等待一段时间后将一页的数据发出,之后再发送确认存储指令10H。发送操作完成之后,Flash开始自动编程,进入等待状态。芯片编程完毕后发送读状态指令,最后查看写操作是否成功。根据芯片的数据手册,同时为了保证数据读取的正确性,在同步工作模式下取CLK平均周期t CK=10 ns,最大页编程操作时间LPROC= 2600![]() 。在这种情况下,单片Flash页编程速度为3.1 MB/s。

。在这种情况下,单片Flash页编程速度为3.1 MB/s。

本系统选用的Flash芯片每个逻辑单元都含有2个plane,因此为了提高单片Flash的页编程速度,本设计采用双plane编程的操作模式,先将第1个plane的写指令和地址写入寄存器,并将数据写入其对应的缓存中,然后将第2个plane重复之前的操作,最后将缓存中的数据一起写入到数据存储区。在双plane页编程下,2个plane操作之间的最短等待时间t DBSY=0.5Ls,此时页编程速度约为5.4 MB/s。双plane编程速度相对于普通的编程速度,提高了将近一倍,由此可以看出,本设计的双plane编程模式优于普通编程模式。

2.1.2 页读取操作

读取操作同样以页为单位进行。普通的单plane页读操作先向命令寄存器写入00H,然后输入5个周期的地址数据,最后写入读指令30H确认数据读出。FPGA通过监测R/B#管脚的输出状态判断读操作是否结束。根据芯片数据手册,在同步工作模式下取t CK= 10 ns,读

一页工作时间t R=75![]() 。单plane操作模式下,读取速度约为27.9 MB/s。

。单plane操作模式下,读取速度约为27.9 MB/s。

针对本次设计,采用双plane的读取结构,先读取第1个plane的控制命令及地址写入寄存器,等状态指示信号R/B#变高以后再读取同一逻辑单元上第2个plane的命令使之进入读操作,最后将所有数据依次读出。在双plane读取的操作模式下,t DBSY=0.5![]() ,t CK= 10 ns,t R=75

,t CK= 10 ns,t R=75 ![]() ,此时读取速度约为31.5 MB/s。相对于普通读操作而言,本设计的双plane读操作模式同样提高了读取速度。

,此时读取速度约为31.5 MB/s。相对于普通读操作而言,本设计的双plane读操作模式同样提高了读取速度。

2.2 Flash并行技术

针对地面检测设备高速大容量的设计,在Flash控制逻辑中通过双plane操作将页编程速度提高为5.4 MB/s,读取速度约为31.5 MB/s。虽然每片Flash包含8个逻辑单元,但是每4个逻辑单元共用一套数据总线,整体速度只能增加4倍,由此看来,仅通过双plane操作模式并没有大幅度提高数据的读写速度,不能满足系统的要求。

为了解决该问题,引入并行总线技术来提高系统的读写速度。并行总线技术是通过扩展带宽的方式有效地提高数据的读写速度。在系统中,引入模块化思想,将Ⅳ片Flash并行连接在数据总线上,它们的片选、控制、读写等信号均相连。并行的这组Flash进行相同的操作,存储容量是单片Flash的N倍,理论上读写速度也是单片Flash的N倍。

根据本系统功能要求,存储速度不低于500 MB/s,而每片Flash的写入速度约为21.6 MB/s,在该情况下,至少需要24片Flash并行操作才能满足系统存储速度的要求。但24片Flash的存储容量达到1.5 GB,超出了系统预期指标太多,从而造成浪费,增加了设计成本。

2.3 Flash流水线技术

单纯地对Flash芯片组采用并行操作虽然可以提高本系统的读写速度,但也增加了设计成本,因此在并行设计的基础上,考虑在减少芯片数量的情况下能够满足系统功能要求的设计方案。

本设计中采用的Flash单个逻辑单元单页编程时间为2600![]() ,而向芯片写入命令、地址时间t CAD=25ns,写入数据时间t DQSS=7.5 ns,这些时间相对编程时间都很短,并且在芯片编程时间内不能对其进行其他的读写操作。因此,充分利用芯片内部编程时间可以大幅度提高数据的写入速度。

,而向芯片写入命令、地址时间t CAD=25ns,写入数据时间t DQSS=7.5 ns,这些时间相对编程时间都很短,并且在芯片编程时间内不能对其进行其他的读写操作。因此,充分利用芯片内部编程时间可以大幅度提高数据的写入速度。

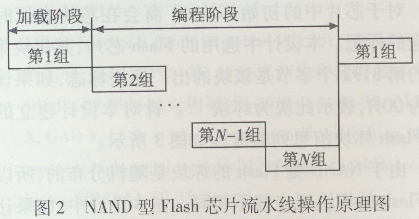

因此,针对本次存储系统,采用流水线设计,当一组Flash芯片编程,不能进行其他操作时,对另外一组芯片进行操作。本设计中NAND型Flash芯片的一个编程周期由数据加载和编程两个阶段组成。一页数据加载时间约为43![]() ,最大编程时间为2600

,最大编程时间为2600![]() ,假设将Flash分成Ⅳ组,加载时间为T1编程时间为T2当满足式(1)时,达到最大编程速度,即

,假设将Flash分成Ⅳ组,加载时间为T1编程时间为T2当满足式(1)时,达到最大编程速度,即

![]()

对应的流水线操作时序如图2所示。

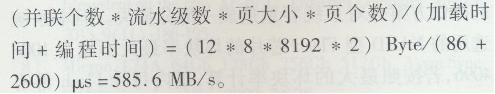

采用双plane编程模式时,加载时间约为86![]() ,此时若令系统达到最大速度最高可采用30级流水操作,速度最大可达到3 GB/s。在本设计中,编程速度达到500 MB/s即可满足系统功能要求,通过分析,系统用12片FIash芯片,芯片分成2组,每组6片并行操

,此时若令系统达到最大速度最高可采用30级流水操作,速度最大可达到3 GB/s。在本设计中,编程速度达到500 MB/s即可满足系统功能要求,通过分析,系统用12片FIash芯片,芯片分成2组,每组6片并行操

作。由于每片Flash含有4个Target,流水级数可达到8级。当采用双plane编程模式时,系统编程速度为:

通过以上分析,本系统共采用12片NAND型Flash芯片,总存储容量为768 GB,理论最高写入速度达到585.6 MB/s。由此可见,采用流水操作控制Flash阵列时,相对于仅采用并行操作技术,节约了一半的芯片数量,但大大提高了编程速度,同时也完全满足本存储系统的技术指标。2.4 Flash坏块管理

本设计中采用的NAND型Flash芯片,虽然读写速度快,但由于它本身包含坏块,并且在使用过程中也会出现新的坏块,这些坏块中的一位或多位均不能正常翻转,因此它们会严重影响数据的存储和读写操作的可靠性。为了提高数据存储系统的可靠性,必须在对Flash的操作过程中屏蔽这些坏块。本设计采用的方法为:对Flash进行读写操作前,首先建立初始坏块列表,记录坏块信息,并且如果在使用过程中出现了新的坏块,及时更新坏块列表信息,避免使用坏块。

在系统结构设计中主控芯片选择XC6SLX100T.该芯片内置丰富的RAM,坏块列表可以存储在这些RAM中,但同时存在掉电后无法获取坏块列表信息的问题,而坏块列表作为保存坏块信息的关键,必须保证其正确存储。与NAND型Flash不同,NOR型Flash虽然不如前者读写速度快,但其可靠性高,芯片中不含坏块,可以保证数据写入的正确性。因此,本设计将坏块列表存储在NOR型Flash中,方便实现更优的坏块管理机制,同时等待上电之后再将列表读入FPGA内置的RAM中,方便对Flash坏块列表信息的调用。

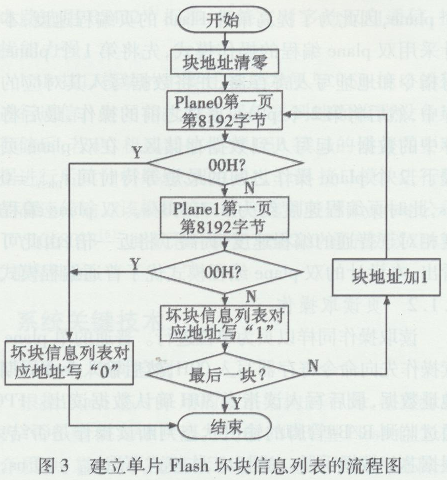

2. 4.1 初始坏块列表的建立

对于芯片中的初始坏块,厂商会在芯片出厂时作相应的标记。本设计中选用的Flash芯片,其每块第一页的第8192个字节是该块的出厂坏块标志,如果该字节为00H,表示此块为坏块。针对本设计建立的单片Flash坏块信息列表流程如图3所示。

由于NAND型Flash的坏块是随机分布的,所以每片Flash的坏块列表都不相同。在本设计中,如果让每片Flash都基于不同的坏块列表进行操作,会占用系统大量的资源,并让系统操作变得复杂。本次设计将12片Flash分成2组,每组6片并行操作,这6片芯片的操作相同,因此将每组内的6片Flash的坏块列表合并,由此建立新的坏块列表。系统采用了并行操作技术,每组6片Flash的读写操作相同。但每片Flash的坏块地址不可能完全相同,因此只要组内的某片Flash的某一块是坏块,就将组内其他Flash的该块都认为是坏块,这样的操作方案会对系统容量造成一部分损失。但本系统选用的NAND型Flash芯片的坏块率最大不超过100/4096,若按照最大的坏块率计算,组内每片Flash都有800个坏块,且位置各不相同,则每组Flash被视为存在28 800个坏块,每块容量为2 MB。整个系统将Flash芯片分成两组,理论上,在最坏的情况下一共会损失112.5GB的容量,但实际中,每片Flash的实际坏块数量不会超过50个,所以整个系统的容量损失不会超过7. 04GB,这在本设计的存储系统中是完全可以接受的。

2.4.2块列表的更新

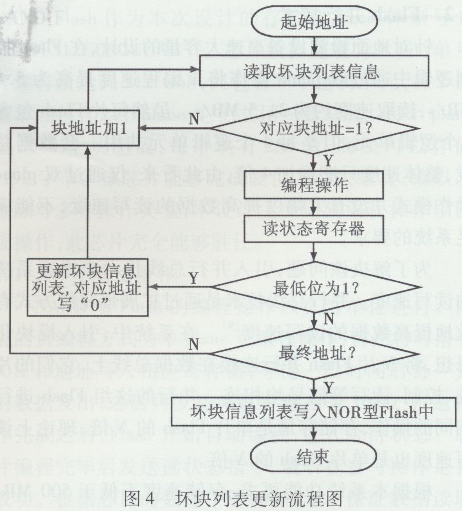

在NAND型Flash芯片使用过程中,如果产生新的坏块,要及时更新坏块列表信息。对Flash进行编程操作以后读取相应状态寄存器,如果其最低位为“1”,则说明编程失败,要将此块标记为坏块。

在Flash出现新的坏块以后,及时更新暂时存放在RAM中的坏块信息,待Flash操作结束之后,将更新的坏块列表写入NOR型Flash中。更新坏块信息列表流程如图4所示。

3 系统验证与分析

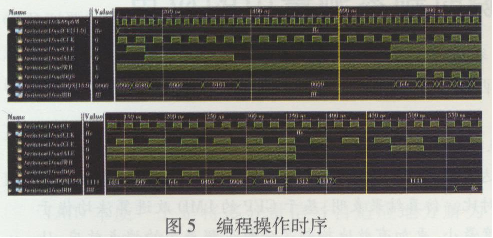

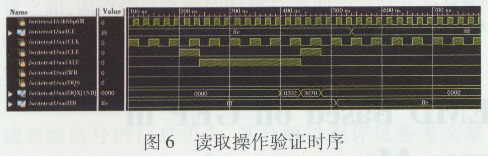

本设计采用Verilog HDL硬件描述语言进行编程,并在Mode lsim环境下进行时序仿真。其中,双plane页编程时序以及页读取时序分别如图5、图6所示。

将系统连接到地面测试台中,令测试台以500 MB/s的速度发送脉冲信号,信号送入存储设备进行实时存储,通过USB2.0接口将数据读出到上位机,其中A/D变换分辨率16位。经过多次测试,测试数据量高达4.3TB yte(l TB yte=1024 GB yte),数据传输速率最高达到550 MB/s,且每次存储的数据均无误码,很好地实现了系统的性能指标。

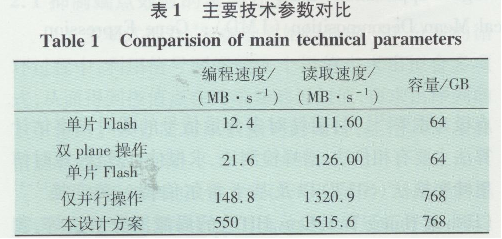

本系统通过采用新型高存储容量NAND型Flash芯片作为存储介质,与以往的空间相机地面存储系统相比,针对系统容量与读写速度的提升,引入了多plane操作、并行及流水线技术等控制Flash存储阵列,在采用存储芯片数量一定的情况下大大提高了系统的读写速度,本系统与未使用以上关键技术的设计参数对比见表1。

以上实验与分析表明,本系统设计方案完全能够满足系统的技术指标。本文对系统引入的坏块管理机制可以在Flash芯片使用过程中有效地屏蔽坏块,大大增加了系统的可靠性。在提出的坏块管理方案中,针对并行的Flash组内的一片Flash出现坏块的情况,把该组每片Flash的该块都做了屏蔽处理,在一定程度上简化了操作方法,但损失了存储系统一部分的存储容量,针对该问题,今后可以考虑更加有效的坏块管理方法。

4结束语

本文在对地面检测设备数据存储设计要求进行分析的基础上,完成了系统总体方案的设计,通过采用NAND型Flash芯片作为存储介质,并引入系统存储的关键技术,包括对Flash芯片的双plane操作、并行操作、流水线技术等,大大提高了系统的存储容量及读写速度。在实际硬件平台上验证了系统的各项功能机制,结果表明,该系统工作稳定可靠,存储容量达到768 GB yte,存储速度最高达到550 MB/s,满足系统设计任务的要求。目前,该系统已成功应用于数据存储任务。